1. Overview

2. 회로의 소신호이득 구하기

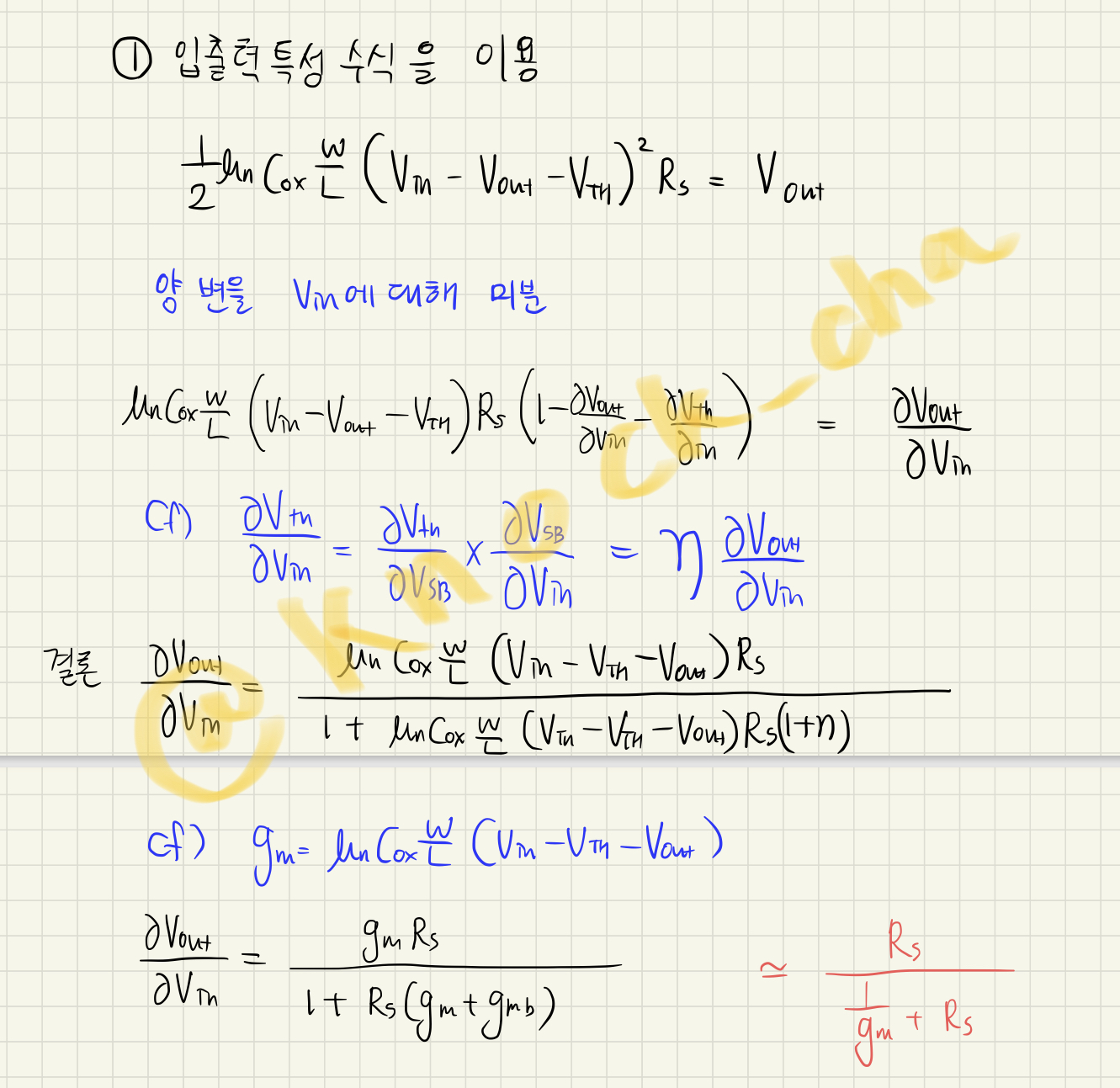

1) I-V 특성으로부터

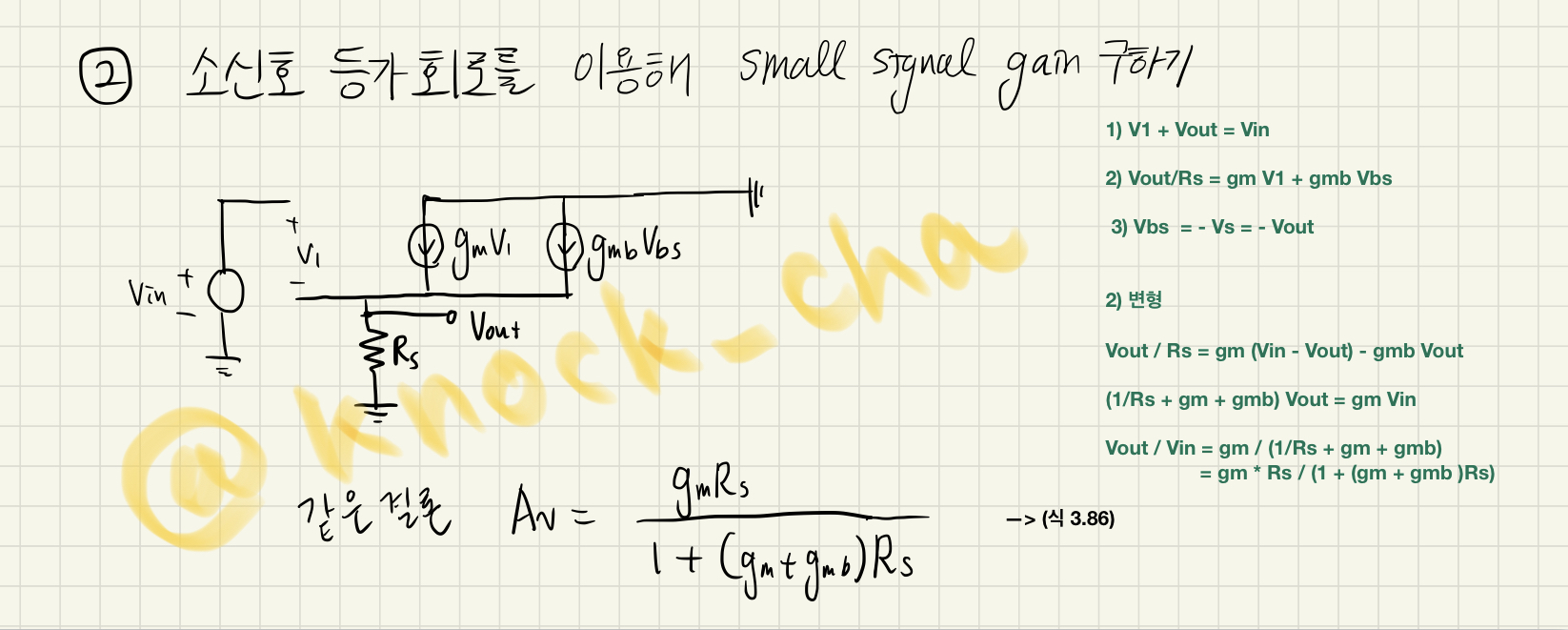

2) SSM (Small Signal Model)로부터

3) analysis

3. 소신호 출력저항

SSM으로부터

4. Body 효과의 영향 & Body 효과를 포함한 SSM

5. SF의 단점(한계)

1) Non Linearity

2) Headroom Limit

3) Rload가 작을 때 (Common Source Stage와 비교)

4) 잡음 증가

1. Overview

유한한 소스 저항을 갖는 구조로부터 공부를 시작한다.

* 소스팔로워는 buffer로서 동작한다.

- impedance matching을 한다.

즉, 낮은 임피던스의 부하 구동시, 전압이득 손실 없이 load를 구동

- 높은 input impedance, 작은 output impedance

* 입출력 특성

- Vout과 Vin은 V_GS 만큼의 차이를 유지하며(level shift), Vout은 Vin을 그대로 따라간다.

V_GS 값은 회로의 bias로서 결정됨.

2. 회로의 소신호이득 구하기 (small signal gain)

1) 입출력 특성으로부터 (Vin - Vout Characteristic)

2) 소신호 등가회로로부터 (SSM = Small Signal Model)

3) Analysis

- 전압이득은 Vin=Vth(gm=0, M1이 켜지기 시작하는 순간)에서부터 시작하여 단조증가 (monotonically increase)한다

- 위에서 구한 소신호 전압이득으로부터, Rs가 무한히 커져도 Av는 1보다 작다.

- Vin이 Vdd + Vth보다만 작으면 M1은 sat영역에 있다.

- gm이 증가하면서 Av는 1/(1+n)으로 수렴.

n은 body effect의 영향으로 Vout이 증가함에 따라 서서히 감소한다. (n = gmb/gm, 혹은 vout에 대한 vth변화율) ==>왜?

하지만 일반적으로 허용 가능한 소오스-벌크 전압(Vout)에 대해서는 n은 대략 0.2보다 큰 값을 유지한다.

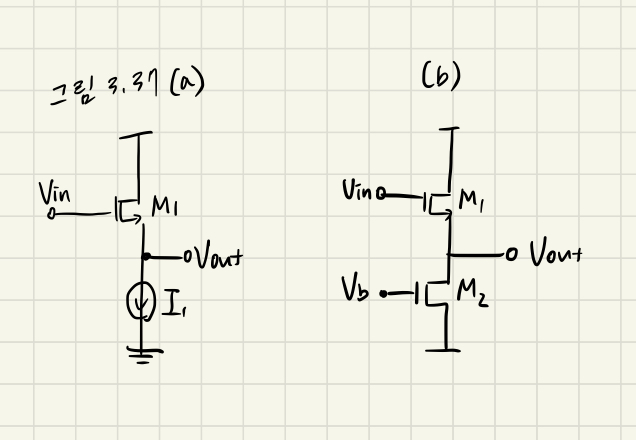

소스팔로워(SF)의 소스단에 저항 대신 이상적인 전류원으로 대체하는 이유 :

- M1의 드레인 전류가 입력 dc수준에 크게 좌우되기 때문이다.

예를 들어 입력전압이 0.7V에서 1V로 변하면, Id는 2배 증가하여 VGS - VTH는 root2배 증가한다. ==> 즉 그만큼 Gate와 Souce 전압과의 차이가 커진다는 뜻

이러한 VGS의 증가는 Vout이 Vin을 충실하게 따라가지 못하는 비선형성을 가져온다.

따라서 이러한 이슈를 제거하기 위해 source단에 저항대신 saturation영역에서 동작하는 NMOS전류원으로 구현한다.

'나홀로 세미나 > 아날로그 CMOS 집적회로 설계' 카테고리의 다른 글

| cascode 캐스코드 3 (1) | 2020.04.21 |

|---|---|

| Cascode 캐스코드 2 (8) | 2020.03.29 |

| Cascode 캐스코드 1 (0) | 2020.03.26 |

| Source Follower 3 (6) | 2020.03.08 |

| Source Follower 2 (4) | 2020.03.03 |