1. Overview

2. 회로의 소신호이득 구하기

1) I-V 특성으로부터

2) SSM (Small Signal Model)로부터

3) analysis

3. 소신호 출력저항

SSM으로부터

4. Body 효과의 영향 & Body 효과를 포함한 SSM

5. SF의 단점(한계)

1) Non Linearity

2) Headroom Limit

3) Rload가 작을 때 (Common Source Stage와 비교)

4) 잡음 증가

5. SF의 단점 ( 한계 )

- 소스팔로워의 장점은 impedance matching. 즉 입력전압을 다음 stage에 잘 전달한다는 점이었다.

- 소스팔로워의 제한(limitation)은 대표적으로 Non-linearity와 전압 헤드룸 제안이 있다.

1) Non Linearity

소스팔로워가 ideal current source에 의해 bias 되어있다고 하더라도, 약간의 비선형성을 보인다.

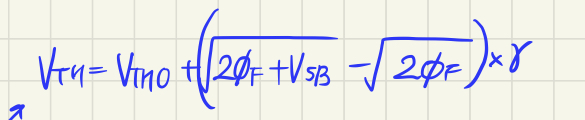

왜냐하면 소스팔로워의 출력은 소스에서 나타나고 이 소스 전압의 변화가 곧 Vth 변화를 일으키기 때문이다.

결과적으로 MOS의 입출력 특성이 Vth특성에 의존하기 때문에 약간의 비선형성을 보인다.

좀더 쉽게 설명을 덧붙이자면,

소스팔로워의 입력인 게이트전압이 증가하면 출력인 소스전압도 정비례하게 증가하는 것이 이상적이다.

하지만, 문턱전압이 소스전압에 root로 비례하여 증가하기 때문에 같은 과구동전압(overdrive voltage, VGS-Vth)를 유지하기 위해서 게이트전압이 계속해서 증가해도 소스전압은 그에 맞는 비율로 높아지지 못한다. (높아진 Vth를 상쇄하기 위해)

따라서 게이트(입력)와 소스(출력)간 비선형성이 생겨버리는 것이다.. (우리가 원하는 동작이 아닐것이다! ㅠ)

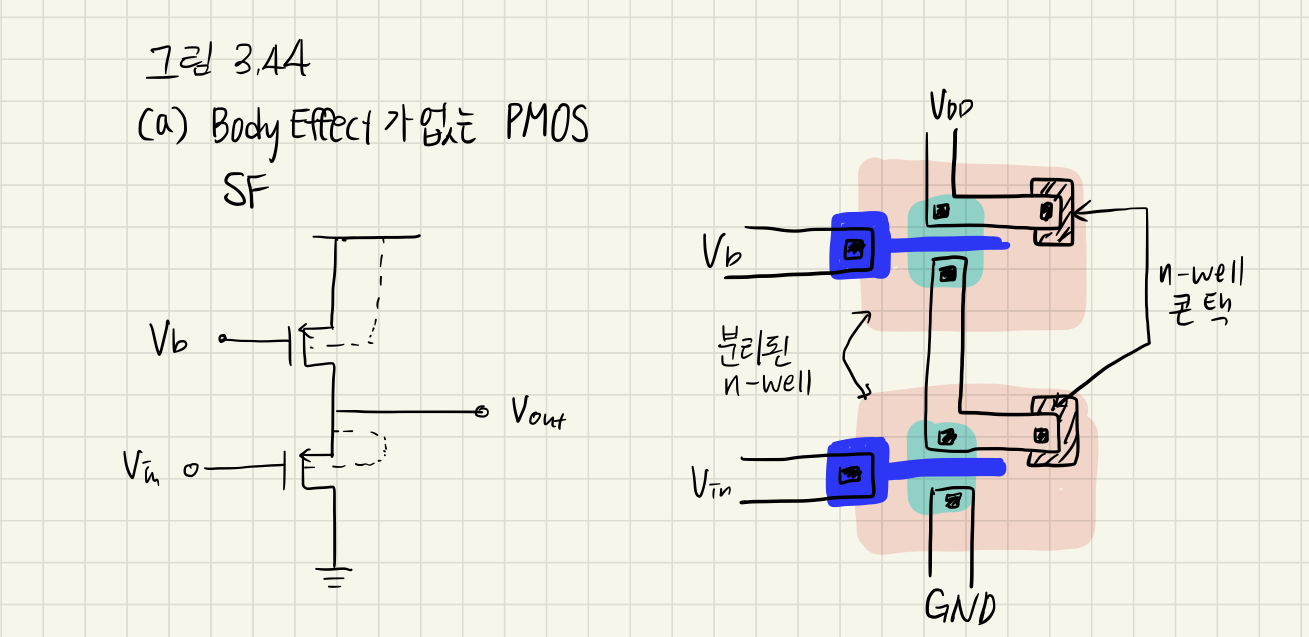

그런데 이런 Body Effect에 따른 비선형성을 해결할 수 있는 아주아주 간단한 방법이 있다!

바로바로 Bulk와 Source 전압을 묶어버리는 것이다!!

그런데 이러한 해결 방법은 일반적으로 PFET에 대해서만 가능하다.

왜냐하면 모든 NFET은 substrate를 공유하므로 개별 NMOS의 Bulk를 특정한 곳에 따로 묶어준다거나 하는것 자체가 불가능하다 ㅠ

2) Voltage Headroom Limit

보통 소스팔로워를 버퍼로서 사용할 때, CS(Common-Source Amp)뒤에 위치시키는 예를 많이 볼 수 있다.

이때, CS의 출력(은 즉 SF의 입력)의 최소 전압(minimum common mode range)은

CS한 단으로 회로가 구성되었을 때보다 소스팔로워의 한개 Vgs만큼 큰 전압을 요구한다.

"즉, 소스팔로워는 VGS만큼의 신호의 dc 수준을 이동시킨다." (CS 회로 입력이 그만큼 더 작아질 것을 요구한다.)

i) 소스팔로워 stage가 없다면?

Vx의 허용 범위 최솟값 : VGS1 - Vth1 ( M1을 saturation 시키기 위한 최소 범위)

ii) 소스팔로워 stage가 있다면?

Vx의 허용 범위 최솟값은 VGS2 + (Vb - Vth3 )보다는 커져야 함.

따라서 M1, M3 과구동전압이 비슷하다 치면, 후자가 VGS2만큼 허용가능한 Vx 스윙이 감소한다.

cf) SF의 또다른 응용(application) DC Voltage level shift

하지만 이런 level shift를 역으로 응용할 수도 있다.

다음 예제를 보자.

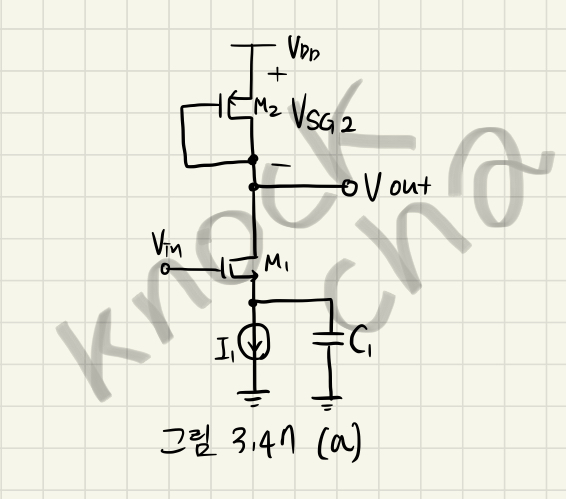

위 그림에서 관심신호의 주파수가 c1을 ac short시킨다고 가정하자.

이때 전압이득과, M1을 saturation에서 동작시키기 위한 input의 max DC level (허용 가능한 최대 DC입력)을 구해보자~~

* Av = -gm1 * ( ro1 // ro2 // (1/gm2) )

cf ) 다이오드 컨넥티드 소자의 드레인에서 바라본 출력 저항이 (ro2 // (1/gm2))임을 상기하자.

* Vin - Vth <= Vout을 만족해야 한다.

따라서 Vin - Vth <= VDD - VSG2

결론 Vin < VDD - VSG2 + Vth

입력은 최대 VDD - VSG2 + Vth까지 커질 수 있다.

그런데 내가 만약 입력을 VDD에 가깝게 더 띄우고 싶다면??? SF를 이용해볼 수 있다!

같은 회로의 앞단에 Source Follower 단을 추가하였다.

M1이 Sat영역에서 동작하는 것을 보장하기 위해, M2와 M3의 VGS의 관계를 어떻게 설정해야하는가?

M1 sat 조건 :

Vx - Vth1 < Vout

Vx - Vth1 < Vdd - VSG2

Vx = Vin - VGS3

위 부등식에 Vx 대입

Vin < VGS3 + Vth1 + Vdd - VSG2

Vin = Vdd를 가정한다면,

VSG2 < VGS3 + Vth1

'나홀로 세미나 > 아날로그 CMOS 집적회로 설계' 카테고리의 다른 글

| cascode 캐스코드 3 (1) | 2020.04.21 |

|---|---|

| Cascode 캐스코드 2 (8) | 2020.03.29 |

| Cascode 캐스코드 1 (0) | 2020.03.26 |

| Source Follower 2 (4) | 2020.03.03 |

| Source Follower 1 (2) | 2020.02.21 |