-캐스코드 토폴로지 (Cascode Topology)

-전압 변화 특성

-캐스코드의 바이어스 조건

-캐스코드의 입출력 특성(대신호 동작)

-캐스코드의 소신호등가회로 & 소신호특성

-캐스코드 토폴로지의 출력저항

-캐스코드 토폴로지 응용

-축소형 캐스코드와 폴디드 캐스코드

파란색 글씨는 저의 개인적인 생각과 견해입니다.

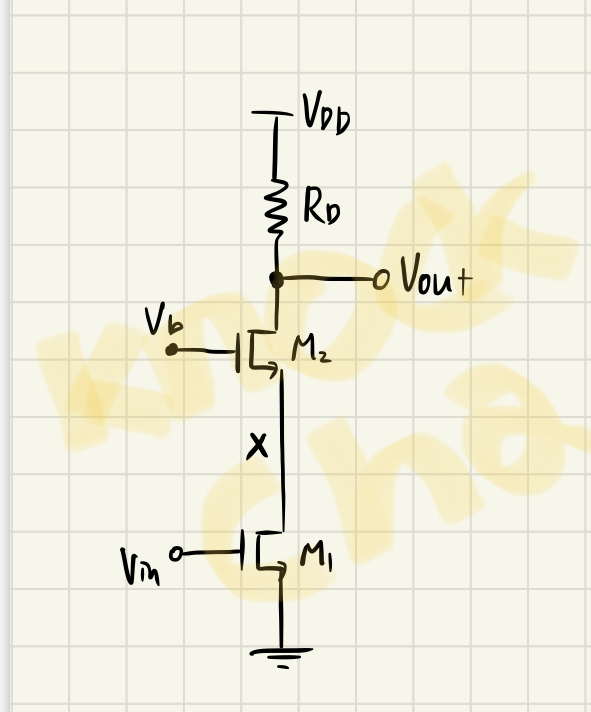

4. 캐스코드의 입출력 특성

이번에는 캐스코드의 입력을 0~Vdd 까지 스윕(sweep) 하여 Vout을 관찰한다. 즉 캐스코드 스테이지의 대신호 입출력 특성을 본다.

1) Vin < Vth

M1 off. 이므로 current path가 끊겨 있다.

따라서 Vout = Vdd이고

Vx는 Vth2 만큼의 전압 강하를 겪는다

Vx = Vb - Vth2 (Vth2는 M2의 게이트에 가했을 때 채널을 형성하기 위한 최소 전압으로 생각하면 됨. 역으로 생각하면 게이트에 일정 전압을 가해도 oxide - silicon 표면에서는 vth만큼 전압이 깎여먹고 보인다는 소리. 따라서 Vb를 가해도 Source쪽에서는 Vth드롭이 보임. == 제가 잘못 알고 있다면 코멘트 부탁드립니다!)

(혹은,, 아주 간단하게 Vx가 Vb-Vth2보다 더 커지면 M2가 turn off 되기 때문이다.)

2) Vin > Vth

M1 turn on -> Vout은 점점떨어진다.

Id1 = Id2로 둘 다 증가하므로, 그에 맞는 전류를 흘리기 위해 Vgs2도 증가한다. ==> 즉 Vx도 떨어진다.

3) Vin이 더 커지면, (i) M1이 triode가 되거나, (ii) M2가 triode가 된다.

(i) M1의 sat 조건은 Vin - Vth1 < Vx이다.

(ii) M2의 sat 조건은 Vb - Vth2 < Vout 이다.

둘 중 어느 것이 먼저 triode로 빠질 지는 소자 크기, Rd, Vb등이 결정한다.

Vb가 크고 Rd가 크다면 Vout이 작아져 M2가 먼저 triode가 될 것이다.

즉 Rd와 Vb는 M2의 동작 영역에 영향을 준다.

하지만 이 모든 것은 상대적인 것이므로.. Vb가 M1의 동작 영역에 직접적으로 영향을 주지 않아도

Vb가 매우 낮다면 M1이 먼저 트라이오드에 진입할 것이다.

소자의 크기가 작다면 (고정된 바이어스 전류를 흘릴 때) Vov (= Vgs - Vth) 가 커진다.

따라서

M2의 크기가 매우 작아진다면 Vx를 그만큼 낮춰주므로 (Vb-Vx증가 그러나 Vb고정이므로) 이때도 M1이 더 빨리 triode에 진입한다.

즉, M2의 크기는 M1의 동작영역에 영향을 준다.

4) M2가 딥 트라이오드 영역으로 들어가면 Vx ~= Vout 이다.

1)~4) 까지 입출력 특성을 그래프로 도시한 것이 아래 그림 3.62 에 나타나있다.

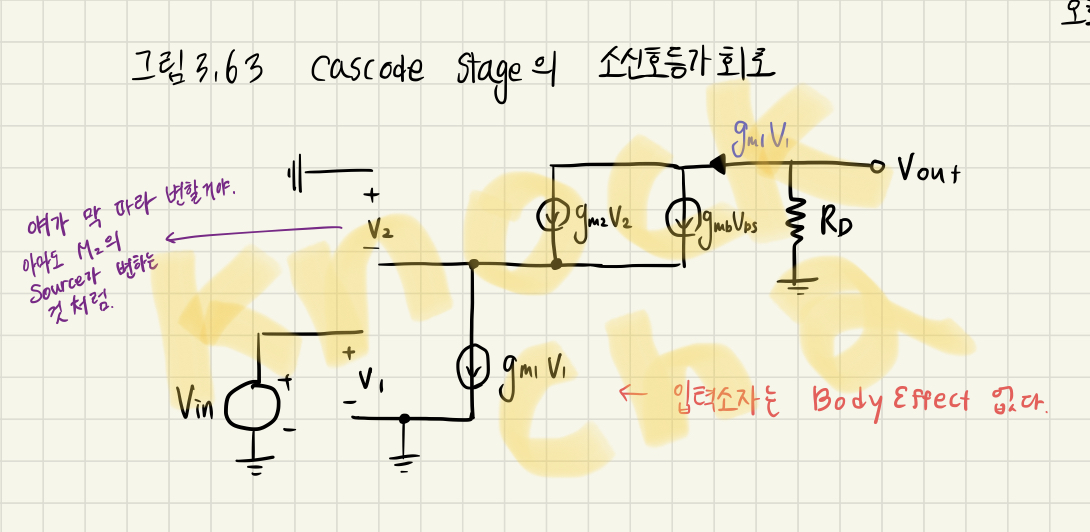

5. 캐스코드의 소신호등가회로 & 소신호특성

- 두 tr이 모두 포화 영역에서 동작한다고 가정

- channel length modulation을 무시한다면, 전압이득은 common - surce 단과 같이 - gm1 Rd 이다.

Av = Gm Rout 모델로도 설명 가능하다.

Channel Length Modulation이 없다면, 캐스코드 단의 전압이득은 입력 소자의 입력에만 영향을 받고

캐스코드 소자의 입력이나 바디이펙트에는 영향을 받지 않는다. ( 전체 전류는 그저 gm1 V1 이므로 )

6. 캐스코드 단의 출력 저항

- 캐스코드 스테이지의 Rout은 ro2와 ro1의 축퇴저항의 직렬 연결로 생각할 수 있다.

R out = ro2 + (1+(gm2+gmb2)ro2) ro1

gm ro >>1 이라고 가정하면 다음과 같이 근사화가 가능하다.

Rout ~= ( gmb2 + gm2 ) ro2 ro1

따라서 캐스코드 구조로 많이 쌓으면 쌓을 수록 출력 저항은 높아지지만,

쌓은 tr개수만큼의 Vov가 전압 헤드룸에서 깎인다.

여태까지 캐스코드 구조의 전압이득이 gm Rd라고 했던 것은

소자의 channel length modulation효과를 무시하여 구했던 것이다.

실제 ro들을 고려하면 캐스코드 구조는 소스단의 ro 축퇴 저항이 보이므로 CS구조보다 큰 출력저항을 갖는다.

Rout ~= ( gmb2 + gm2 ) ro2 ro1 을 고려한 소신호 전압이득은

Av ~= ( gmb2 + gm2 ) gm1 ro2 ro1 으로 ,, 대략 tr의 intrinsic gain의 제곱과 같다.

'나홀로 세미나 > 아날로그 CMOS 집적회로 설계' 카테고리의 다른 글

| cascode 캐스코드 4 (0) | 2020.05.17 |

|---|---|

| cascode 캐스코드 3 (1) | 2020.04.21 |

| Cascode 캐스코드 1 (0) | 2020.03.26 |

| Source Follower 3 (6) | 2020.03.08 |

| Source Follower 2 (4) | 2020.03.03 |