-캐스코드 토폴로지 (Cascode Topology)

-전압 변화 특성

-캐스코드의 바이어스 조건

-캐스코드의 입출력 특성(대신호 동작)

-캐스코드의 소신호등가회로 & 소신호특성

-캐스코드 토폴로지의 출력저항

-캐스코드 토폴로지 응용

- 추가) Shielding Property

-축소형 캐스코드와 폴디드 캐스코드

파란색 글씨는 저의 개인적인 생각과 견해입니다.

7. 캐스코드 토폴로지의 응용

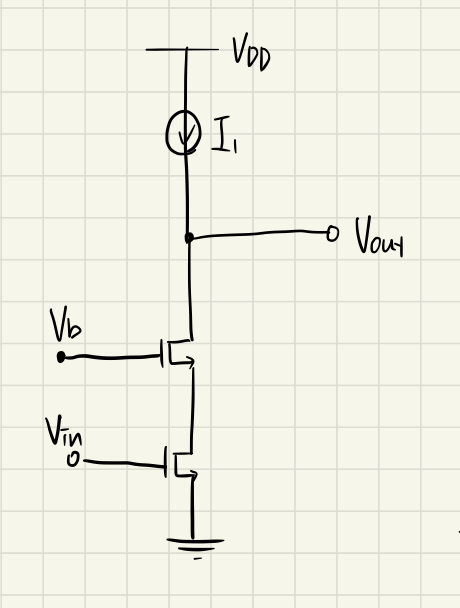

캐스코드 구조는 증폭기말고 Constant Current Source (정전류원)으로서 응용될 수 있다.

우리가 회로에서 이상적인 전류원의 출력 저항은 무한대로 생각한다.

왜냐하면 양단의 전압이 바뀌어도 일정한 전류를 흘려주기 때문이다. (V=IR 공식을 생각하면 쉽다.)

이처럼 출력저항이 높은 캐스코드 구조는 이상적인 전류원을 설계할 때 이용한다는 아이디어를 이해할 수 있다.

반면에 그것에 대한 trade-off로 전압 헤드룸의 대가를 치러야 한다.

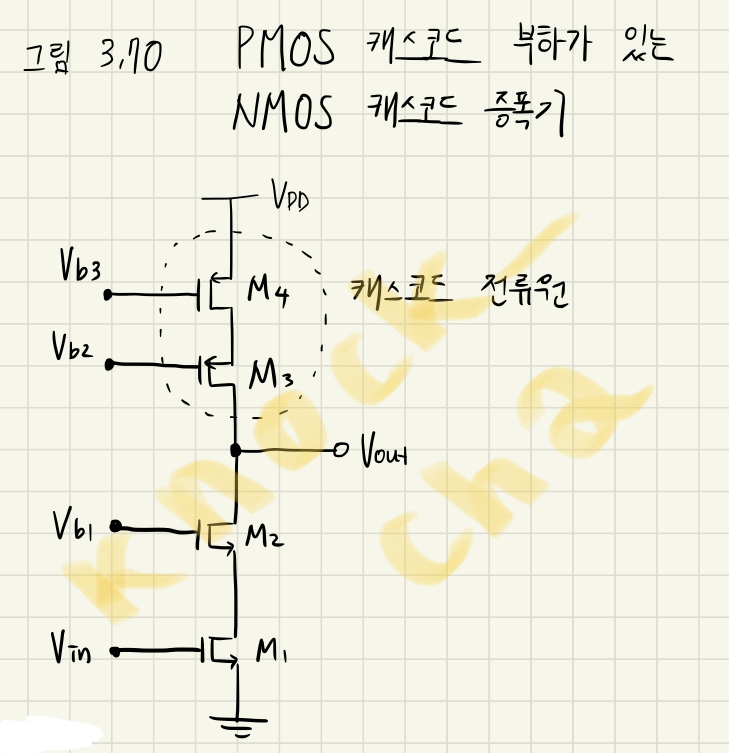

위 그림에서의 전류원은 PMOS캐스코드 구조로 아래 그림과 같이 구현될 수 있으며,

그 임피던스는 ro3와 degenerated (축퇴된) ro4 을 고려하여 계산할 수 있다.

즉 PMOS 캐스코드 부분의 임피던스는 ro3 + (1+(gm3+gmb3))ro4

아래 NMOS 캐스코드 부분의 임피던스도 똑같이 구할수있음.

따라서 위 회로의 출력 임피던스는 Rout = { ro3 + (1+(gm3+gmb3)ro3)ro4 } // { ro2 + (1+(gm2+gmb2)ro2)ro1 }

전압이득 Av = gm1 * Rout으로 구할 수 있다. Rout을 단순화하여 근사하면

Av = gm1 * ( [gm3 ro3 ro4] // [gm2 ro2 ro1] )

8. 캐스코드의 차폐특성 (shielding property )

shielding property

1. 모스 Tr의 축퇴 성질을 생각하면 보다 직관적인 이해를 얻을 수 있다.

모스펫의 드레인에서 소스쪽을 바라보면 소스쪽 저항은 축퇴되어 (1 + gm ro)만큼 뻥튀기되어 보인다.

이는 drain에서 바라본 출력저항이 단순히 ro와 Rs(소스쪽 저항) 의 직렬 연결이 아니라 이보다 훨씬 크게 보인다는 것을 뜻하며,

저항이 크다는 것은 출력(drain)에서의 전압 변화에 비해 Drain-Source를 통해 흐르는 전류 변화가 매우 작음을 의미한다.

다시 말해, 드레인에서의 전압 변화가 saturation 상태에서 동작하는 MOS소자의 특성(gm)에 영향을 주지 않는다고 해석할 수 있다.

2. 캐스코드 구조의 경우에, 회로의 gm을 결정하는 입력소자는 캐스코드 소자의 소스 아래에 위치한다.

위와 설명대로 MOS의 특징을 생각해보면,

캐스 코드 소자의 드레인 단에 연결된 어떤 아날로그 시스템이 캐스코드 소자의 드레인에 출렁이는 전압을 공급하여도

입력소자는 캐스코드 소자의 소스 단에 위치하고 있기 때문에, 이에 대한 영향을 받지 않고 보호받는다고 해석하였다.

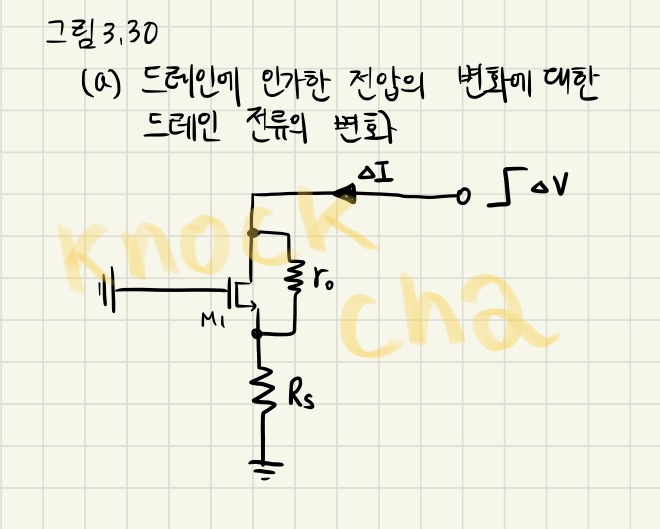

1.에 관한 설명

드레인에서의 전압 변화가 초래하는 드레인으로 흘러들어가는 전류의 변화가 매우 작다.

즉 드레인에서 바라본 저항은 매우 크다는 것은, 드레인에서 소스단 저항을 바라볼 때 축퇴되어 보이는 것을 증명하여 보일 수 있다.

출력 저항 (ro와 소스축퇴저항) 구하기.

드레인 출력쪽에서 바라본 저항을 구하려고 하므로, M1의 입력은 접지시킨다.

소신호 출력저항을 구하는 것이므로 드레인단에서 전압 변화를 ΔV로 나타내었다. 이때의 ΔI를 구해서 나눈 다음 R을 구할것임.

ΔV가 MOS 드레인과 ro에 똑같이 전해지므로, 그 노드를 쪼개고 두 노드에 같은 전압 변화를 주는 것처럼 쪼갠 등가 회로를 그릴 수 있다.

그 그림이 아래 그림 (b)이다.

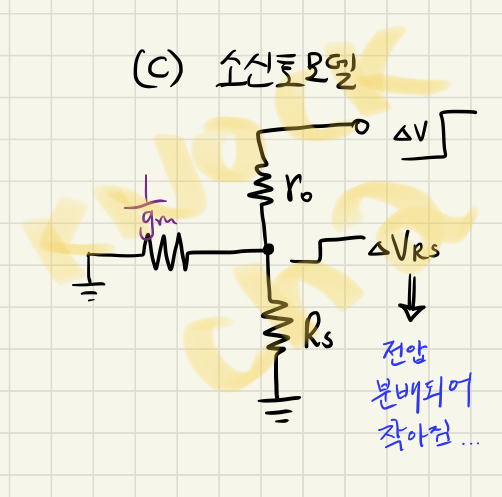

M1의 source에서 바라본 저항을 1/gm으로 볼 수 있으므로, 그림 (c)와 같은 소신호모델을 을 그릴 수 있다.

이때 ΔV가 Rs에 전해지는 전압인 ΔVRS를 전압 분배법칙을 이용하여 구하면

ΔVRS = {1+gm // Rs + ro} / {1/gm // Rs + ro}

Rs를 통하여 흐르는 전류의 변화가 ΔI이므로

ΔI = ΔVRS / RS

ΔI = ΔV / {ro + gm ro Rs +Rs }

따라서 Rout = ro + (1+ gm ro ) Rs

이므로 드레인에서 바라본 출력 저항은 ro와 Rs(1+ gm ro)의 직렬 연결처럼 보인다.

즉 소스단 Rs가 축퇴되었다고 한다.

저는 이 축퇴 성질을 이해하고, 2. 를 다시 읽어보면 더 다채로운 이해를 할 수 있었습니다.

'나홀로 세미나 > 아날로그 CMOS 집적회로 설계' 카테고리의 다른 글

| cascode 캐스코드 4 (0) | 2020.05.17 |

|---|---|

| Cascode 캐스코드 2 (8) | 2020.03.29 |

| Cascode 캐스코드 1 (0) | 2020.03.26 |

| Source Follower 3 (6) | 2020.03.08 |

| Source Follower 2 (4) | 2020.03.03 |