-캐스코드 토폴로지 (Cascode Topology)

-전압 변화 특성

-캐스코드의 바이어스 조건

-캐스코드의 입출력 특성(대신호 동작)

-캐스코드의 소신호등가회로 & 소신호특성

-캐스코드 토폴로지의 출력저항

-캐스코드 토폴로지 응용

- 추가) Shielding Property

-축소형 캐스코드와 폴디드 캐스코드

파란색 글씨는 저의 개인적인 생각과 견해입니다.

9. 축소형 캐스코드와 폴디드 캐스코드

이번 포스팅에서는 조금 특이한 구조의 캐스코드 토폴로지 응용들을 살펴본다!

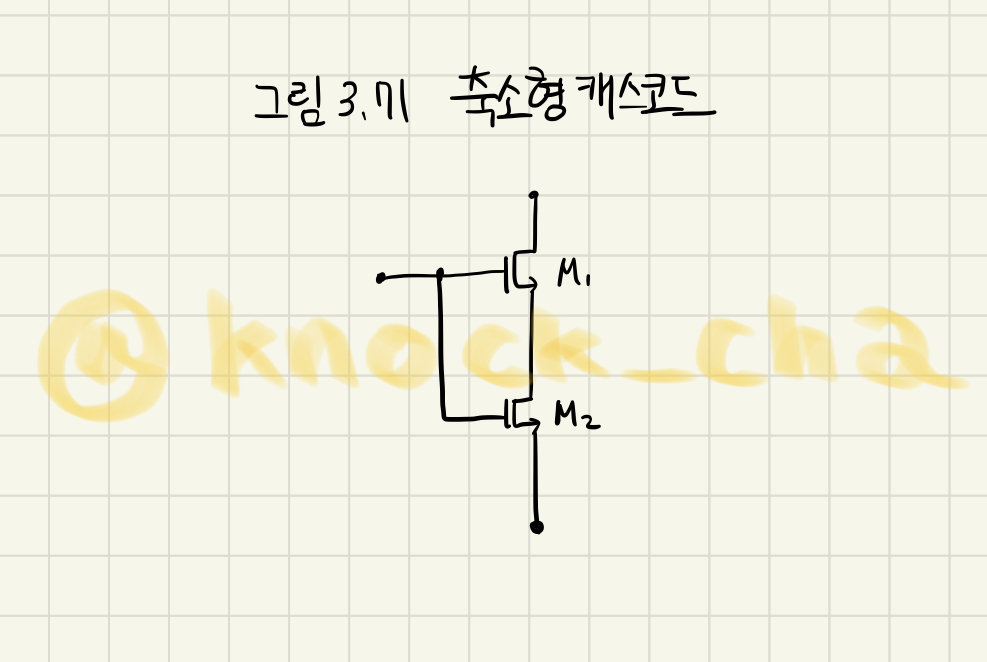

1) 축소형 캐스코드 (minimalist cascode)

- poor man's cascode라고 함

- M2는 트라이오드 영역에서 동작한다.

M1 이 turn on 되려면 gate 전압이 Source 전압보다 Vth만큼 커야한다.

그런데 M1의 Source는 M2의 드레인이므로, 위 조건에 따르면 M2의 드레인이 Vg + Vth보다 작아야 함.

따라서 M2는 Saturation이 아닌 linear 영역에서 동작한다.

그러나 어떤 공정에서 두 개의 tr의 vth를 다르게 사용할 수 있다면 진정한 캐스코드로서 동작 가능하다!

- 사실 저 구조는 gate length를 합친 하나의 transistor와 등가이다. (tr의 series연결 => L을 합한 것과 같음)

2) Folded Cascode 폴디드 캐스코드

*캐스 코드 구조의 아이디어 : 입력소자는 입력 전압을 전류로 바꾸고, 그 결과를 common-gate단에 가한다.

* 위 아이디어를 차용하면서 구조를 변형! 생각의 전환! : 입력소자와 캐스코드 소자는 반드시 같은 type일 필요가 없다!

아래 그림처럼 M1 PMOS 로 입력을 받아 전환한 전류를 M2 NMOS Common Gate에 통과 시키자!

바이어스가 안 잡혔으므로 아래 그림처럼 수정해보자.

소신호 동작

잠시 이 폴디드 캐스코드 구조의 소신호 동작을 살펴보면,

1. vin 증가

2. ID1감소 (PMOS 이므로)

3. ID2 증가 (바이어스 전류 I1으로 일정하므로) (X전압 감소)

4. Vout 감소

--> vin과 Vout은 반대 극성이다.

반대로 NMOS입력 PMOS캐스코드 소자인 캐스코드 토폴로지도 아래처럼 구성할 수 있다.

폴디드 캐스코드와 일반 캐스코드의 차이점 :

일반 캐스코드에서는 M1의 바이어스 전류가 M2에도 재사용되어 흐르는 반면,

폴디드 캐스코드에선 M1과 M2의 바이어스 전류가 I1으로 합쳐진다.

즉 같은 성능을 내기 위해 folded cascode의 바이어스 전류 I1은 그냥 캐스코드에서보다 커져야 한다. (바이어스 전류를 두 MOS tr이 나누어 씀..) 대신, Voltage swing range (전압 헤드룸) 측면에서 Folded Cascode가 낫기 때문에 이 구조를 쓸 것이다!... 는 나의 생각

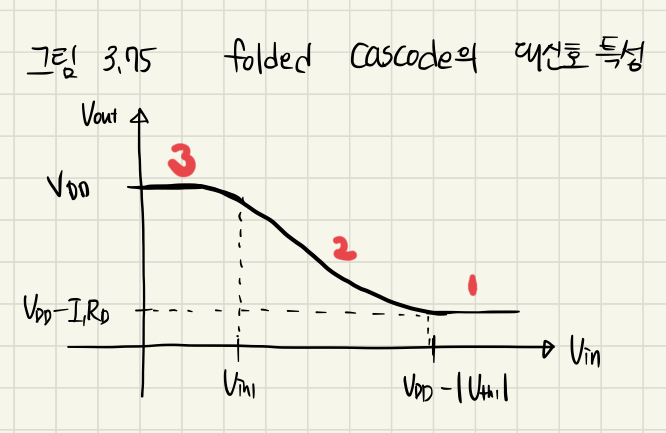

Folded Cascode의 대신호 동작 :

Vin을 VDD에서 0V까지 Sweep 해가며 대신호 동작을 살펴본다.

1) Vin > Vdd - |Vth1|

M1 off.

모든 전류가 M2로 흐름

Vout = Vdd - I1 Rd

2) Vin < Vdd - |Vth1|

M1 on ( sat region에서 시작 )

Id2 = I1 - Id1

= I1 - 1/2 k'(w/l)1 (Vdd-Vin -|Vth1|)^2

3) Vin이 더 작아져서 Id2가 더더욱 감소하여 0이되게하는 (즉, Id1 = I1) Vin을 구할 수 있다.

I1 = 1/2 k' (w/l)1 (Vdd - Vin - |Vth1|) ^2

Vin = Vdd - root (2I1 / k'(w/l)1) - |Vth1|

이때, Vout = Vdd

4) 만약 Vin이 더 Vin1보다 더 감소하여 Id1이 I1보다 더 큰 전류를 흘리고자 한다면,

Id1 = I1을 위해 M1은 triode 영역으로 들어간다. (Vin 게이트가 x노드 Drain보다 너무 낮아져 버린거임!!!!!)

cf) Id1 = Id2가 되게 하는 Vin2를 구할 수도 있는데,

1/2 I1 = 1/2 k' (w/l) (Vdd - Vin2 - |Vth1|)^2

식을 풀면,

Vin2 = Vdd - root ( I1 / k'(w/l) ) - |Vth1|

5) Vx의 관전에서 보면 무슨 일이 일어날까요

x노드는 잘 보면 , M1의 드레인이자 M2의 소스이다.

두 tr이 saturation영역이라면, 전류 크기에 영향을 미치는 것은 gate와 source 노드 사이의 전압이다!!!

따라서, I2가 감소함에 따라 Vx는 증가한다 (Vgs감소)

Id2 = 0에서는 Vb-Vth2로 최대 값을 갖는다.

Vin이 더 감소하여 M1이 triode영역으로 들어가면, M1의 드레인도 I1을 결정짓는 큰 요소가 된다. 따라서 딥 트라이오드 영역으로 갈 수록, Vx는 Vdd에 근접한다.

'나홀로 세미나 > 아날로그 CMOS 집적회로 설계' 카테고리의 다른 글

| cascode 캐스코드 3 (1) | 2020.04.21 |

|---|---|

| Cascode 캐스코드 2 (8) | 2020.03.29 |

| Cascode 캐스코드 1 (0) | 2020.03.26 |

| Source Follower 3 (6) | 2020.03.08 |

| Source Follower 2 (4) | 2020.03.03 |